設(shè)計(jì)一款CPU到底有多難 集成電路設(shè)計(jì)的挑戰(zhàn)

設(shè)計(jì)一款中央處理器(CPU)是集成電路領(lǐng)域中極具挑戰(zhàn)性的任務(wù),涉及復(fù)雜的工程、科學(xué)和商業(yè)考量。從概念到成品,整個(gè)過程需要耗費(fèi)數(shù)年時(shí)間、數(shù)十億美元的資金,以及多學(xué)科團(tuán)隊(duì)的緊密協(xié)作。以下是CPU設(shè)計(jì)的主要難點(diǎn)。

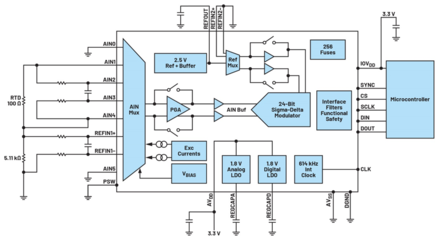

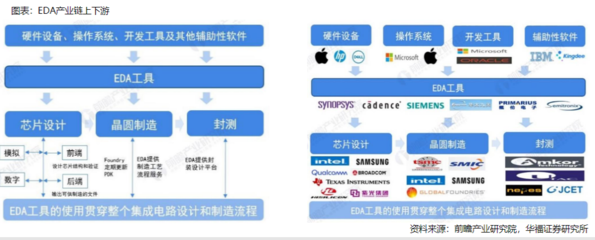

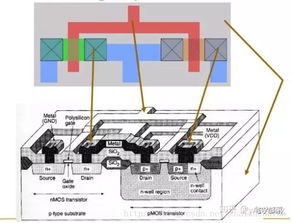

CPU設(shè)計(jì)需要極高的技術(shù)復(fù)雜性。CPU作為計(jì)算機(jī)的‘大腦’,必須處理指令、執(zhí)行計(jì)算并管理數(shù)據(jù)流。設(shè)計(jì)者需考慮指令集架構(gòu)(如x86或ARM),確保兼容性、性能和功耗平衡。現(xiàn)代CPU包含數(shù)十億個(gè)晶體管,每個(gè)晶體管的位置和連接都必須精確設(shè)計(jì),這需要先進(jìn)的電子設(shè)計(jì)自動化(EDA)工具,以及深入的半導(dǎo)體物理知識。

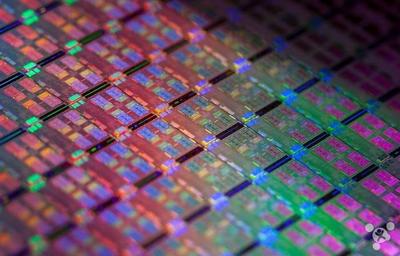

工藝和制造是另一大難關(guān)。CPU設(shè)計(jì)完成后,必須通過光刻等工藝在硅片上制造。隨著工藝節(jié)點(diǎn)不斷縮小(如從14納米到5納米以下),設(shè)計(jì)者面臨量子效應(yīng)、熱管理和信號完整性問題。任何微小錯(cuò)誤都可能導(dǎo)致芯片失效,造成巨大損失。制造過程依賴于全球供應(yīng)鏈,從晶圓廠到封裝測試,每個(gè)環(huán)節(jié)都需要嚴(yán)格質(zhì)量控制。

第三,驗(yàn)證和測試是CPU設(shè)計(jì)的瓶頸。由于CPU功能繁多,設(shè)計(jì)團(tuán)隊(duì)必須進(jìn)行全面的仿真和測試,以確保無錯(cuò)誤。這包括功能驗(yàn)證、性能分析和功耗評估,通常需要構(gòu)建原型芯片,并運(yùn)行數(shù)百萬個(gè)測試用例。據(jù)估計(jì),驗(yàn)證階段可能占整個(gè)項(xiàng)目時(shí)間的70%以上,稍有疏忽就可能導(dǎo)致產(chǎn)品召回或市場失敗。

市場和時(shí)間壓力加劇了難度。CPU市場競爭激烈,公司如英特爾、AMD和ARM不斷推出新產(chǎn)品。設(shè)計(jì)周期長,而技術(shù)更新快,團(tuán)隊(duì)必須在性能、成本和上市時(shí)間之間找到平衡。新興應(yīng)用如人工智能和物聯(lián)網(wǎng)對CPU提出了新需求,要求設(shè)計(jì)更具靈活性和能效。

設(shè)計(jì)一款CPU是集成電路設(shè)計(jì)的巔峰挑戰(zhàn),它融合了電子工程、計(jì)算機(jī)科學(xué)和材料學(xué)等多領(lǐng)域知識。盡管難度巨大,但成功的CPU能推動技術(shù)進(jìn)步,改變世界。對于設(shè)計(jì)者來說,這是一場耐力與創(chuàng)新的馬拉松。

如若轉(zhuǎn)載,請注明出處:http://m.eaco-capacitor.com/product/19.html

更新時(shí)間:2026-02-20 12:17:46